nios2.h

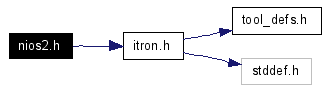

#include <itron.h>nios2.hのインクルード依存関係図

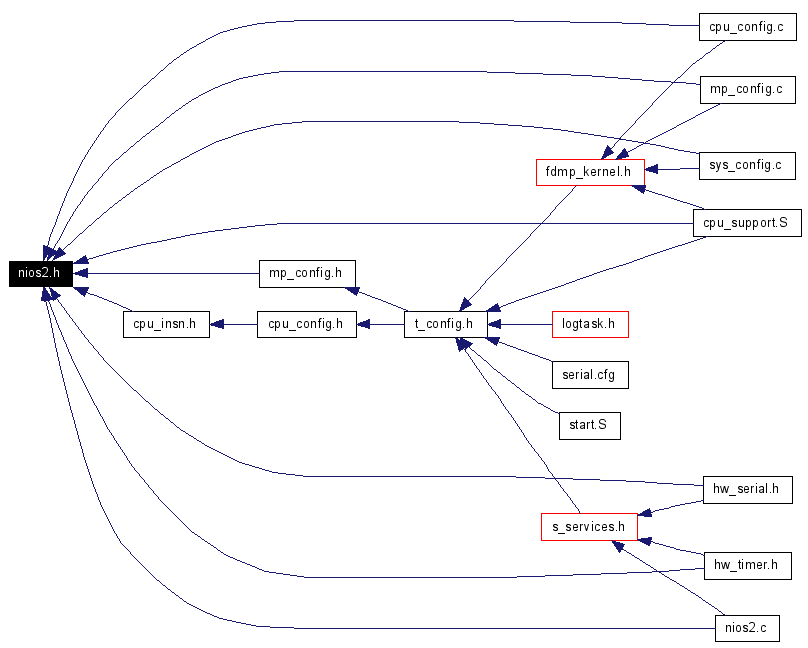

このグラフは、どのファイルから直接、間接的にインクルードされているかを示しています。

データ構造 | |

| struct | sio_port_initialization_block |

| struct | sio_port_control_block |

マクロ定義 | |

| #define | STATUS_U 0x02 |

| #define | STATUS_PIE 0x01 |

| #define | MAX_INT_NUM 32 |

| #define | MAX_EXC_NUM 32 |

| #define | TIM_STATUS_OFFSET 0x00 |

| #define | TIM_CONTROL_OFFSET 0x04 |

| #define | TIM_PERIODL_OFFSET 0x08 |

| #define | TIM_PERIODH_OFFSET 0x0C |

| #define | TIM_SNAPL_OFFSET 0x10 |

| #define | TIM_SNAPH_OFFSET 0x14 |

| #define | TIM_STATUS_RUN 0x02 |

| #define | TIM_STATUS_TO 0x01 |

| #define | TIM_CONTROL_STOP 0x08 |

| #define | TIM_CONTROL_START 0x04 |

| #define | TIM_CONTROL_COUNT 0x02 |

| #define | TIM_CONTROL_ITO 0x01 |

| #define | TIM_STATUS (TIM_BASE + TIM_STATUS_OFFSET) |

| #define | TIM_CONTROL (TIM_BASE + TIM_CONTROL_OFFSET) |

| #define | TIM_PERIODL (TIM_BASE + TIM_PERIODL_OFFSET) |

| #define | TIM_PERIODH (TIM_BASE + TIM_PERIODH_OFFSET) |

| #define | TIM_SNAPL (TIM_BASE + TIM_SNAPL_OFFSET) |

| #define | TIM_SNAPH (TIM_BASE + TIM_SNAPH_OFFSET) |

| #define | UART_RXDATA_OFFSET 0x00 |

| #define | UART_TXDATA_OFFSET 0x04 |

| #define | UART_STATUS_OFFSET 0x08 |

| #define | UART_CONTROL_OFFSET 0x0C |

| #define | UART_DIVISOR_OFFSET 0x10 |

| #define | UART_ENDOFPACKET_OFFSET 0x1C |

| #define | UART_STATUS_EOP 0x1000 |

| #define | UART_STATUS_CTS 0x0800 |

| #define | UART_STATUS_DCTS 0x0400 |

| #define | UART_STATUS_E 0x0100 |

| #define | UART_STATUS_RRDY 0x0080 |

| #define | UART_STATUS_TRDY 0x0040 |

| #define | UART_STATUS_TMT 0x0020 |

| #define | UART_STATUS_TOE 0x0010 |

| #define | UART_STATUS_ROE 0x0008 |

| #define | UART_STATUS_BRK 0x0004 |

| #define | UART_STATUS_FE 0x0002 |

| #define | UART_STATUS_PE 0x0001 |

| #define | UART_CONTROL_IEOP 0x1000 |

| #define | UART_CONTROL_RTS 0x0800 |

| #define | UART_CONTROL_IDCTS 0x0400 |

| #define | UART_CONTROL_TRDK 0x0200 |

| #define | UART_CONTROL_IE 0x0100 |

| #define | UART_CONTROL_IRRDY 0x0080 |

| #define | UART_CONTROL_ITRD 0x0040 |

| #define | UART_CONTROL_ITMT 0x0020 |

| #define | UART_CONTROL_ITOE 0x0010 |

| #define | UART_CONTROL_IROE 0x0008 |

| #define | UART_CONTROL_IBRK 0x0004 |

| #define | UART_CONTROL_IFE 0x0002 |

| #define | UART_CONTROL_IPE 0x0001 |

| #define | UART_RXDATA (UART_BASE + UART_RXDATA_OFFSET) |

| #define | UART_TXDATA (UART_BASE + UART_TXDATA_OFFSET) |

| #define | UART_STATUS (UART_BASE + UART_STATUS_OFFSET) |

| #define | UART_CONTROL (UART_BASE + UART_CONTROL_OFFSET) |

| #define | UART_DIVISOR (UART_BASE + UART_DIVISOR_OFFSET) |

| #define | UART_ENDOFPACKET (UART_BASE + UART_ENDOFPACKET_OFFSET) |

| #define | JTAG_UART_DATA_OFFSET 0x00 |

| #define | JTAG_UART_CONTROL_OFFSET 0x04 |

| #define | JTAG_UART_DATA_RVALID 0x8000 |

| #define | JTAG_UART_CONTROL_RIE 0x01 |

| #define | JTAG_UART_CONTROL_WIE 0x02 |

| #define | JTAG_UART_CONTROL_RIP 0x04 |

| #define | JTAG_UART_CONTROL_WIP 0x08 |

| #define | JTAG_UART_CONTROL_WSAPCE 0x0ffff0000 |

| #define | JTAG_UART_DATA (UART_BASE + JTAG_UART_DATA_OFFSET) |

| #define | JTAG_UART_CONTROL (UART_BASE + JTAG_UART_CONTROL_OFFSET) |

| #define | MUTEX_MUTEX_OFFSET 0x00 |

| #define | MUTEX_RESET_OFFSET 0x04 |

| #define | MUTEX_MUTEX_OWNER_MASK 0xffff0000 |

| #define | MUTEX_MUTEX_VALUE_MASK 0x0000ffff |

| #define | MUTEX_MUTEX_OWNER_OFFSET (16) |

| #define | MUTEX_RESET_RESET_MASK 0x01 |

| #define | MUTEX_VALUE_DATA 0x1234 |

| #define | uart_openflag (siopcb_table[0].openflag) |

| #define | SIO_ERDY_SND 1u |

| #define | SIO_ERDY_RCV 2u |

型定義 | |

| typedef sio_port_initialization_block | SIOPINIB |

| typedef sio_port_control_block | SIOPCB |

関数 | |

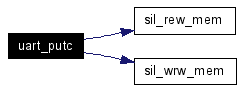

| Inline void | uart_putc (unsigned char c) |

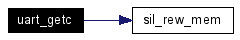

| Inline unsigned char | uart_getc (void) |

| void | uart_initialize (void) |

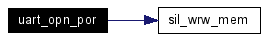

| SIOPCB * | uart_opn_por (ID siopid, VP_INT exinf) |

| void | uart_cls_por (SIOPCB *siopcb) |

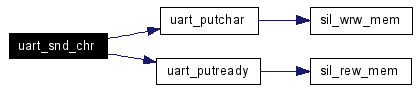

| BOOL | uart_snd_chr (SIOPCB *siopcb, INT chr) |

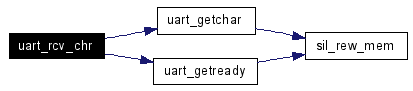

| INT | uart_rcv_chr (SIOPCB *siopcb) |

| void | uart_ena_cbr (SIOPCB *siopcb, UINT cbrtn) |

| void | uart_dis_cbr (SIOPCB *siopcb, UINT cbrtn) |

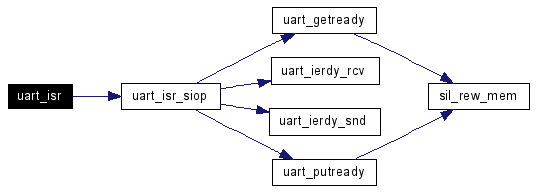

| void | uart_isr (void) |

| void | uart_ierdy_snd (VP_INT exinf) |

| void | uart_ierdy_rcv (VP_INT exinf) |

| Inline int | mutex_try_lock (unsigned int addr, unsigned int id) |

| Inline void | mutex_unlock (unsigned int addr, unsigned int id) |

| Inline void | mutex_init (unsigned int addr, unsigned int id) |

変数 | |

| SIOPCB | siopcb_table [] |

マクロ定義

|

|

参照元 uart_cls_por()・uart_disable_rcv()・uart_disable_send()・uart_enable_rcv()・uart_enable_send()・uart_opn_por()・uart_putc()・uart_putready(). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

参照元 uart_getc()・uart_getchar()・uart_getready()・uart_putc()・uart_putchar(). |

|

|

|

|

|

|

|

|

|

|

|

参照元 cpu_initialize(). |

|

|

|

|

|

参照元 mutex_init(). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

参照元 mutex_try_lock(). |

|

|

|

|

|

参照元 serial_snd_chr()・sio_ierdy_snd()・uart_dis_cbr()・uart_ena_cbr(). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

参照元 hw_timer_fetch_interrupt()・hw_timer_initialize()・hw_timer_int_clear()・hw_timer_terminate(). |

|

|

|

|

|

|

|

|

|

|

|

参照元 uart_cls_por()・uart_disable_rcv()・uart_disable_send()・uart_enable_rcv()・uart_enable_send()・uart_opn_por(). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

参照元 uart_getc()・uart_getready()・uart_opn_por()・uart_putc()・uart_putready(). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

参照元 uart_disable_rcv()・uart_enable_rcv()・uart_getc()・uart_getready()・uart_opn_por(). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

型定義

|

|

|

|

|

|

関数

|

||||||||||||

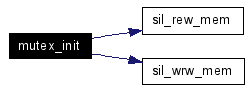

|

参照先 MUTEX_MUTEX_OFFSET・MUTEX_MUTEX_OWNER_MASK・MUTEX_MUTEX_OWNER_OFFSET・MUTEX_RESET_OFFSET・MUTEX_RESET_RESET_MASK・sil_rew_mem()・sil_wrw_mem(). 参照元 init_obj_lock()・init_tsk_lock(). 00323 { 00324 unsigned int data; 00325 unsigned int check; 00326 00327 check = sil_rew_mem((VP)(addr + MUTEX_RESET_OFFSET)); 00328 00329 //リセットがされたかのチェック 00330 if ( check == MUTEX_RESET_RESET_MASK ){ 00331 sil_wrw_mem((VP)(addr + MUTEX_RESET_OFFSET), MUTEX_RESET_RESET_MASK); 00332 } 00333 else { 00334 data = sil_rew_mem((VP)(addr + MUTEX_MUTEX_OFFSET)); 00335 sil_wrw_mem((VP)(addr + MUTEX_MUTEX_OFFSET), (data & MUTEX_MUTEX_OWNER_MASK)); 00336 sil_wrw_mem((VP)(addr + MUTEX_MUTEX_OFFSET), (id << MUTEX_MUTEX_OWNER_OFFSET)); 00337 } 00338 }

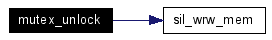

関数の呼び出しグラフ:  |

|

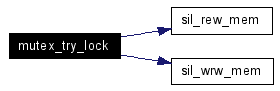

||||||||||||

|

参照先 MUTEX_MUTEX_OFFSET・MUTEX_MUTEX_OWNER_OFFSET・MUTEX_VALUE_DATA・sil_rew_mem()・sil_wrw_mem(). 参照元 local_acquire_lock(). 00293 { 00294 unsigned int data; 00295 unsigned int check; 00296 00297 data = (id << MUTEX_MUTEX_OWNER_OFFSET) | MUTEX_VALUE_DATA; 00298 00299 sil_wrw_mem((VP)(addr + MUTEX_MUTEX_OFFSET), data); 00300 check = sil_rew_mem((VP)(addr + MUTEX_MUTEX_OFFSET)); 00301 00302 if ( data == check ){ 00303 return 1; 00304 } 00305 else { 00306 return 0; 00307 } 00308 }

関数の呼び出しグラフ:  |

|

||||||||||||

|

参照先 MUTEX_MUTEX_OFFSET・MUTEX_MUTEX_OWNER_OFFSET・MUTEX_RESET_OFFSET・MUTEX_RESET_RESET_MASK・sil_wrw_mem(). 参照元 local_release_lock(). 00314 { 00315 sil_wrw_mem((VP)(addr + MUTEX_RESET_OFFSET), MUTEX_RESET_RESET_MASK); 00316 sil_wrw_mem((VP)(addr + MUTEX_MUTEX_OFFSET), (id << MUTEX_MUTEX_OWNER_OFFSET)); 00317 }

関数の呼び出しグラフ:  |

|

|

参照先 FALSE・JTAG_UART_CONTROL・sio_port_control_block::openflag・sio_port_control_block::sendflag・sil_wrw_mem()・UART_CONTROL. 参照元 sio_cls_por(). 00246 { 00247 #ifndef USE_JTAG_UART 00248 /* 割込み禁止 */ 00249 sil_wrw_mem((VP)UART_CONTROL, 0x00); 00250 #else 00251 sil_wrw_mem((VP)JTAG_UART_CONTROL,0x00); 00252 #endif /* USE_JTAG_UART */ 00253 siopcb->openflag = FALSE; 00254 siopcb->sendflag = FALSE; 00255 }

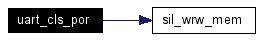

関数の呼び出しグラフ:  |

|

||||||||||||

|

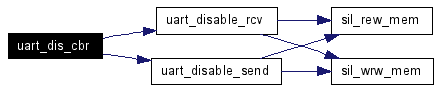

参照先 SIO_ERDY_RCV・SIO_ERDY_SND・uart_disable_rcv()・uart_disable_send(). 00315 { 00316 switch (cbrtn) { 00317 case SIO_ERDY_SND: 00318 uart_disable_send(siopcb); 00319 break; 00320 case SIO_ERDY_RCV: 00321 uart_disable_rcv(siopcb); 00322 break; 00323 } 00324 }

関数の呼び出しグラフ:  |

|

||||||||||||

|

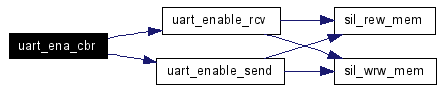

参照先 SIO_ERDY_RCV・SIO_ERDY_SND・uart_enable_rcv()・uart_enable_send(). 00298 { 00299 switch (cbrtn) { 00300 case SIO_ERDY_SND: 00301 uart_enable_send(siopcb); 00302 break; 00303 case SIO_ERDY_RCV: 00304 uart_enable_rcv(siopcb); 00305 break; 00306 } 00307 00308 }

関数の呼び出しグラフ:  |

|

|

参照先 JTAG_UART_DATA・JTAG_UART_DATA_RVALID・sil_rew_mem()・UART_RXDATA・UART_STATUS・UART_STATUS_RRDY. 00211 { 00212 #ifndef USE_JTAG_UART 00213 while(!(sil_rew_mem((VP)UART_STATUS) & UART_STATUS_RRDY)); 00214 return (char)(sil_rew_mem((VP)UART_RXDATA)); 00215 #else 00216 int tmp; 00217 do{ 00218 tmp = sil_rew_mem((VP)JTAG_UART_DATA); 00219 }while((tmp &JTAG_UART_DATA_RVALID) == 0); 00220 00221 return (char)tmp; 00222 #endif /* USE_JTAG_UART */ 00223 }

関数の呼び出しグラフ:  |

|

|

参照元 uart_isr_siop(). |

|

|

参照元 uart_isr_siop(). |

|

|

参照先 FALSE・sio_port_control_block::openflag・sio_port_control_block::sendflag・siopcb_table・sio_port_control_block::siopinib・siopinib_table・TNUM_SIOP. 00203 { 00204 SIOPCB *siopcb; 00205 UINT i; 00206 00207 /* 00208 * シリアルI/Oポート管理ブロックの初期化 00209 */ 00210 for (siopcb = siopcb_table, i = 0; i < TNUM_SIOP; siopcb++, i++) { 00211 siopcb->siopinib = &(siopinib_table[i]); 00212 siopcb->openflag = FALSE; 00213 siopcb->sendflag = FALSE; 00214 } 00215 }

|

|

|

参照先 siopcb_table・uart_isr_siop(). 00352 { 00353 if (siopcb_table[0].openflag) { 00354 uart_isr_siop(&(siopcb_table[0])); 00355 } 00356 }

関数の呼び出しグラフ:  |

|

||||||||||||

|

参照先 sio_port_control_block::exinf・FALSE・get_siopcb・sio_port_control_block::getready・JTAG_UART_CONTROL・JTAG_UART_CONTROL_RIE・sio_port_control_block::openflag・sio_port_control_block::putready・sil_wrw_mem()・sio_port_control_block::siopinib・TRUE・UART_CONTROL・UART_STATUS・UART_STATUS_RRDY. 参照元 sio_opn_por(). 00218 { 00219 00220 SIOPCB *siopcb; 00221 const SIOPINIB *siopinib; 00222 00223 siopcb = get_siopcb(siopid); 00224 siopinib = siopcb->siopinib; 00225 00226 #ifndef USE_JTAG_UART 00227 // sil_wrw_mem(UART_DIVISOR, UART_DIVISOR_VAL); 00228 sil_wrw_mem((VP)UART_STATUS, 0x00); 00229 00230 /* 00231 * 受信割り込み許可 00232 */ 00233 sil_wrw_mem((VP)UART_CONTROL, UART_STATUS_RRDY); 00234 #else 00235 sil_wrw_mem((VP)JTAG_UART_CONTROL,JTAG_UART_CONTROL_RIE); 00236 #endif /* USE_JTAG_UART */ 00237 00238 siopcb->exinf = exinf; 00239 siopcb->getready = siopcb->putready = FALSE; 00240 siopcb->openflag = TRUE; 00241 00242 return(siopcb); 00243 }

関数の呼び出しグラフ:  |

|

|

参照先 JTAG_UART_CONTROL・JTAG_UART_CONTROL_WSAPCE・JTAG_UART_DATA・sil_rew_mem()・sil_wrw_mem()・UART_STATUS・UART_STATUS_TRDY・UART_TXDATA. 参照元 sys_putc(). 00199 { 00200 #ifndef USE_JTAG_UART 00201 while(!(sil_rew_mem((VP)UART_STATUS) & UART_STATUS_TRDY)); 00202 sil_wrw_mem((VP)UART_TXDATA, c); 00203 #else 00204 while(!((sil_rew_mem((VP)JTAG_UART_CONTROL) & JTAG_UART_CONTROL_WSAPCE) > 0)); 00205 sil_wrw_mem((VP)JTAG_UART_DATA, c); 00206 #endif /* USE_JTAG_UART */ 00207 00208 }

関数の呼び出しグラフ:  |

|

|

参照先 uart_getchar()・uart_getready(). 00275 { 00276 #ifndef USE_JTAG_UART 00277 if (uart_getready(siopcb)) { 00278 return((INT)(UB) uart_getchar(siopcb)); 00279 } 00280 return(-1); 00281 #else 00282 UB tmp; 00283 00284 if (jtag_uart_buf != -1) { 00285 tmp = jtag_uart_buf; 00286 jtag_uart_buf = -1; 00287 return tmp; 00288 } 00289 return(-1); 00290 #endif /* USE_JTAG_UART */ 00291 }

関数の呼び出しグラフ:  |

|

||||||||||||

|

参照先 FALSE・TRUE・uart_putchar()・uart_putready(). 00262 { 00263 if(uart_putready(siopcb)){ 00264 uart_putchar(siopcb, (UB) chr); 00265 return(TRUE); 00266 } 00267 return(FALSE); 00268 }

関数の呼び出しグラフ:  |

変数

|

|

|

Copyright © 2006 by TAKAGI Nobuhisa.

このページは Mon Apr 3 23:49:17 2006 に Doxygen によって生成されました。